# 1 ビジョンシステムの実用化に関する研究開発(第3報)

佐野 誠,武田幹雄,石津任章,馬場祥宏,土井貴広\*,神長大輔\*\*,大亀勝久\*\*\*,森合雅朗\*\*\*

Research and Development about Utilization of Vision System (3rd Report)

SANO Makoto, TAKEDA Mikio, ISHIZU Hideaki, BABA Yoshihiro, DOI Takahiro\*, KAMINAGA Daisuke\*\*

OHGAME Katsuhisa\*\*\* and MORIAI Masaaki\*\*\*

Recently, image processing IP is frequently used for vision system such as product inspection. But when the IP is used, the IP is improved to modify for the specification s of the vision system. The IP has so much information about the electronic circuit that it is difficult to improve the IP. This paper presents the new type of image processing IP with a very useful structure. User doesn't need to improve the new type of the IP, when the IP is used in the vision system.

キーワード:画像処理, IP,パイプライン回路,穀粒判別器,画像処理ボード,マウスポインタ制御装置

## 1 緒 言

広島県産業科学技術研究所・岩田プロジェクト(「リアルタイム物体・空間認識」プロジェクト)(平成12年度~14年度)の成果の一つである画像処理IPを成果普及する目的で,平成15年度から3年間研究開発を進めてきた。本報告はその第3報であり,これまでの成果をまとめて報告する。また,画像処理IPの応用展開として,眼球の動きを位置情報に変換し,パソコンの操作を補助するマウスポインタ制御装置を開発中であり,試作段階であるので概要について説明する。

## 2 **画像処理** IP

### 2.1 **画像処理 IP の種類**

これまでに開発した 20 種類の汎用的な画像処理 IP を表 1 に示す。最高動作周波数 , ロジックセル数 , 使用 RAM ビット数は 実装する FPGA 等のデバイスにより異なるが , 表中の値は AI tera 社 EP1C12Q240C8 で算出している。これらの IP は濃淡画像処理 IP として有償で提供している。

#### 2.2 **画像処理パイプライン回路**

画像処理 IP を利用する場合の特徴を説明するために, CPU 単独による処理,画像処理 IP 単独による処理,CPU と画像処理 IP を組み合わせたときの処理をそれぞれ図1 に示す。

CPU のみによる画像処理の場合は,まず画像取り込み

表 1 画像処理 IP の性能

| IP の種類               | 最高動作<br>周 波 数 | ロジック<br>セ ル 数 | RAM<br>ビット数 |

|----------------------|---------------|---------------|-------------|

| X軸・Y軸射影(*)           | 89MHz         | 129           | 14336       |

| 周囲長(*)               | 111MHz        | 99            | 1024        |

| 面積(2値)(*)            | 275MHz        | 21            | 0           |

| 重心(2値)(*)            | 197MHz        | 85            | 0           |

| フィレ径(2値)(*)          | 183MHz        | 107           | 0           |

| 慣性等価楕円の傾き角(2値)(*)    | 165MHz        | 292           | 0           |

| 膨張・収縮                | 114MHz        | 52            | 2048        |

| ラベリング                | 42MHz         | 772           | 94208       |

| 面積(濃淡)               | 93MHz         | 120           | 5120        |

| 重心(濃淡)               | 77MHz         | 390           | 15360       |

| フィレ径(濃淡)             | 72MHz         | 288           | 10240       |

| 慣性等価楕円の傾き角(濃淡)       | 75MHz         | 809           | 30720       |

| 濃度ヒストグラム(*)          | 92MHz         | 120           | 5120        |

| 階調変換                 | 197MHz        | 4             | 2048        |

| 3×3空間フィルタ            | 89MHz         | 1408          | 16384       |

| 3×3差分型エッジ検出フィルタ      | 89MHz         | 2626          | 16384       |

| 画像間演算(加算、減算、比較)      | 275MHz        | 106           | 0           |

| 抵抗ヒューズネットワーク         | 78MHz         | 967           | 51968       |

| 膨張・収縮8段              | 87MHz         | 324           | 16384       |

| メディアンフィルタ            | 62MHz         | 414           | 16384       |

| *・2 値画像加理 ID レルプ右償担併 |               |               |             |

\*:2 値画像処理 IP として有償提供

を行い、これが終了してから処理が開始される。各単機能(図中の処理1~処理6)の処理時間は速いが逐次的に処理される。これに対して画像処理 IP の場合は、画像を取り込む過程で処理を施すことができ、その単機能処理をつなげてパイプライン構成とすることで、並列処理が可能となる(図中の処理1~処理4)。そのため、パイプラインの段数が増えるほど、CPU に対して相対的に高速に

<sup>\*</sup>株式会社サタケ, \*\*株式会社インタフェース,

<sup>\*\*\*</sup>株式会社システムアートウェア

なる。また,画像処理 IPとCPUの利点を組み合わせるとさらに高速になる。加えて,ハードウェアをFPGAで実現すると,画像処理 IPの柔軟性と再利用性という特徴が活かされ,高速で柔軟性がある画像処理を構築できる<sup>1),2)</sup>。

CPU

画像取り込み 処理1

処理2

処理3

処理4

処理5 処理6

画像処理IP + CPU

処理4

処理5

処理6

動像処理IP + CPU

処理2

処理4

処理5

処理3

処理6

処理6

処理3

処理7

処理4

処理5

回像処理IP

CPU

処理時間

#### 図 1 画像処理 IP のパイプライン構成

このように画像処理 IPを活用することで高速化を実現することができるが,設計の点から見た場合,画像処理 IP の追加,削除および順序の変更を行う時には,画像処理 IP 以外に周辺回路の設計変更(接続部分の変更)が必要になる。その変更部分を設計するためには,画像処理 IP の回路仕様を理解する必要があるので,ユーザには負担である。

そこで、このような問題点を解決するために、画像処理 IP の追加、削除および順序の変更を行うと、接続部分が自動的に生成されるような設計支援ソフトウェアと、自動生成に適した構造を有するパイプラインの構成法を開発した。本画像処理パイプライン回路の構成法と接続部分の自動生成機構に関して特許を出願した³)。このパイプライン機能付きの濃淡画像処理 IP も有償提供している。

#### 3 画像処理 IP の成果展開

#### 3.1 マウスポインタ制御装置

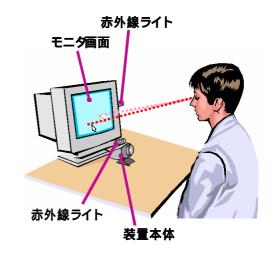

パソコンのインターフェースデバイス(キーボード,マウスなど)は,手指による操作が要求されるので肢体不自由者などには不向きである。そこで,眼球の動き(視線)を位置情報に変換してパソコンの操作を補助する,マウスポインタ制御装置の開発を進めている<sup>4)</sup>。操作イメージを図2に示す。カメラで瞳を撮影し,その画像から視線方向を算出し,この結果を元に画面上のマウスカーソルを制御してパソコンの操作を行う。文字入力は,図3に示すような画面上の仮想キーボード(専用アプリ

ケーション)によって行う。開発中の試作ボードの外観を**図**4に示す。

図2 操作イメージ

図3 文字入力用の仮想キーボード画面

#### 3.2 卓上型穀粒判別器

図1に示したように,画像処理 IPと CPU の処理を組み合わせることでそれぞれの長所を活かし,高速化を実現することができる。図5は,県内企業と共同で開発した卓上型穀粒判別器であり,画像処理 IPと CPU を組み合わせて高速化した。この判別器は穀粒の良・不良を判定するとともに,穀粒を選り分ける機能が付いた判別器である。

図 5 卓上型穀粒判別器 (RGQI-20A)

#### 3.3 濃淡画像処理ボード

図6は、画像処理 IP を実装した濃淡画像処理ボードで、PCI バス用、Compact PCI バス用の種類がある。県内企業と共同で開発した。ソフトウェア上で画像処理 IP の機能を選択することが可能である。

図 6 **濃淡画像処理ボード (**PCI-5533)

#### 4 結 言

これまでの3年間に画像処理IPの開発とその応用展開を行った。以下にまとめる。

- 1)画像処理に必須の汎用的な画像処理 IP を 20 種類開発 した。

- 2)画像処理パイプライン回路を考案した。 ユーザが IP の

仕様を把握しなくても回路設計ができる仕様になって おり,パイプラインの構成法と接続部分の自動生成機 構に関して特許を出願した。

- 3)選別機能を持った卓上型穀粒判別器に画像処理 IP を 活用して製品化した。

- 4) 濃淡画像処理 PCI ボードおよび Compact PCI ボードに 画像処理 IP を活用して製品化した。

- 5)遺伝的アルゴリズムを応用して,画像処理アルゴリズムの作成を支援するソフトウェアを開発した<sup>3)</sup>。

- 6) 眼球の動きを位置情報に変換して , パソコンの操作を 補助するマウスポインタ制御装置を開発中である<sup>4)</sup>。 装置の小型化 ,マイコン負荷の軽減に画像処理 IP を活 用している。

本研究では、画像処理 IPの開発と応用展開を図ることで、LSI (FPGA)の設計、開発、実装技術を構築した。LSI設計分野の進展はめざましく、HDL (ハードウェア記述言語)による回路設計から、C言語ベースの動作・機能設計へと移行しつつある。LSI はあらゆる分野の製品に組み込まれており、製品の小型化、高機能化、高速化には欠かせない技術である。今後も LSI や電子回路設計の研究開発に取り組んでいく予定である。

# 文 献

1)石津他:平成14年度研究成果報告書,広島県産業科学技術研究所,2003

2) 佐野他: 広島県立西部工技研究報告, No47(2004),1 3) 佐野他: 広島県立西部工技研究報告, No48(2005),1 4) 武田他: 広島県立西部工技研究報告, No48(2005),60